Tanks a lot! Pg 58

Call me unconvinced by USB 3.0 Pg 6

Signal Integrity: Making Gaussian edges Pg 16

**Design Ideas** Pg 39

**Supply Chain** Pg 52

Product Innovation from Cirrus Logic

64-PIN QFP, PACKAGE STYLE HQ JEDEC MO-188

(actual footprint)

#### **NORTH AMERICA**

+1 800-625-4084

#### **ASIA PACIFIC**

+852 2376-0801

#### **JAPAN**

+81 (3) 5226-7757

#### EUROPE/UK

+44 (0) 1628-891-300

# Protection = Performance Over Current Short Circuit Thermal Protection Cycle-by-Cycle Current Limit Undervoltage Lockout OSP or MCU PWM Controller Brushless DC Motor Protection

#### 3 A, Three-Phase Motor Driver IC Uses Protection Features to Deliver Performance Gains

The SA303-IHZ is a pulse width modulation (PWM) motor driver IC designed to protect brushless motors from operational hazards such as over current, under voltage and over temperature. This newest addition to the Apex Precision Power® product family can generate performance gains in the overall motor control circuitry by eliminating motor shutdown and re-starts. For example, should an over-temperature or short circuit occur, the SA303-IHZ will not shutdown the outputs but instead allows the system to continue running while it signals the external controller to take corrective action. In most cases, the processor can correct the condition by utilizing software to remedy the external interrupt.

#### **APPLICATIONS**

- Motor Drives Industrial Controls

- Factory Automation

- Robotics

- Motor Drives Office Equipment

- Copiers, Fax Machines

- Vending Machines

- Motor Drives Aerospace, Military

- Positioning Control

- Aircraft Seating

| Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Motor<br>Interface    | Output<br>Current           | Supply Voltage<br>Operation    | Production<br>Volume Pricing<br>10K Pieces USD* |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------------|--------------------------------|-------------------------------------------------|--|

| SA303-IHZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Brushless<br>DC Motor | 3 A continuous<br>10 A Peak | 10 V to 60 V<br>Single Supply  | \$5.86                                          |  |

| SA306-IHZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Brushless<br>DC Motor | 5 A continuous<br>17 A PEAK | < 9 V to 60 V<br>Single Supply | \$9.90                                          |  |

| SA306A-FHZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Brushless<br>DC Motor | 8 A continuous<br>17 A PEAK | < 9 V to 60 V<br>Single Supply | \$12.85                                         |  |

| SA53-IHZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Brush<br>DC Motor     | 3 A continuous<br>10 A Peak | 10 V to 60 V<br>Single Supply  | \$4.79                                          |  |

| SA57-IHZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Brush<br>DC Motor     | 5 A continuous<br>17 A PEAK | < 9 V to 60 V<br>Single Supply | \$7.15                                          |  |

| SA57A-FHZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Brush<br>DC Motor     | 8 A continuous<br>17 A PEAK | < 9 V to 60 V<br>Single Supply | \$9.05                                          |  |

| # to a total of a contract of a contract of a contract of a contract of a tractical of a contract of a con |                       |                             |                                |                                                 |  |

$<sup>^{\</sup>star}$  per unit pricing for production estimating only; actual per unit cost through distribution may vary

#### **REQUEST A FREE SAMPLE!**

Request a free sample unit of the SA303-IHZ By visiting www.cirrus.com/sa303edn

For product selection assistance or technical support with Apex Precision Power products call 1-800-546-2739 or apex.support@cirrus.com.

LEARN MORE AT www.cirrus.com/sa303edn

Over 400,000 products in stock from more than 400 supplier partners.

An additional 1,000,000+ components can be sourced at digikey.com

The industry's broadest product selection available for immediate delivery

www.digikey.com 1.800.344.4539

#### "How can I tell if a power supply is reliable?"

#### There's an indicator on the front.

It says "Agilent." With a typical MTBF of 40,000 hours, over half-acentury of experience, and with more than 250 models to choose from, Agilent's power supplies are the ones you can count on. In fact the array of our power supplies is so extensive, it wouldn't fit on this page. For clean, low-noise, programmable power to countless DUTs, there's an Agilent power supply with your name on it. Actually, it's our name on it, but you know what we mean.

For free measurement tips and the Agilent Power Products brochure go to www.agilent.com/find/powertips

Agilent Authorized Distributors

Hensley

Instrument Engineers

877-595-7447

800-444-6106

© 2009 Agilent Technologies, Inc.

# EDN 12.3.09 contents

#### Microinverters and power optimizers

Alternative forms of power have become increasingly popular as utilities react to rising fuel prices and government mandates. Photovoltaic cells usually receive most of the attention as solar-energy cost drivers, but the ac/dc inverter design is equally important to overall system efficiency and cost.

> by Margery Conner, Technical Editor

#### The evolving landscape of digital signal processing

The continual evolution of microprocessors is one of the causes of a trend away from stand-alone DSPs.

> by Robert Cravotta, Technical Editor

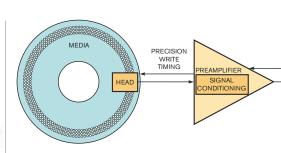

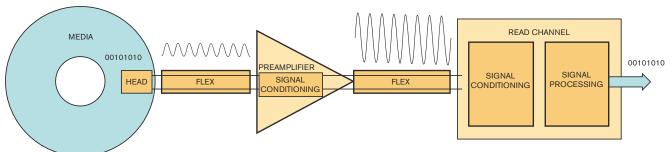

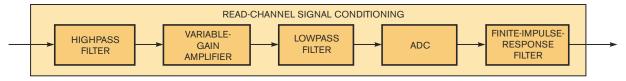

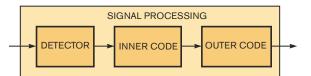

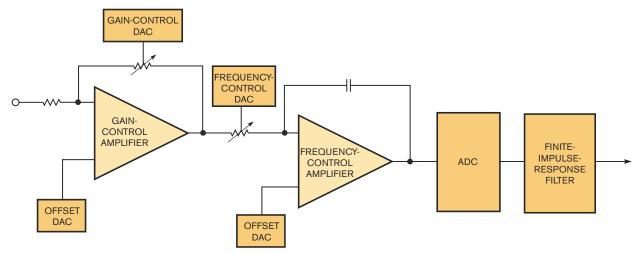

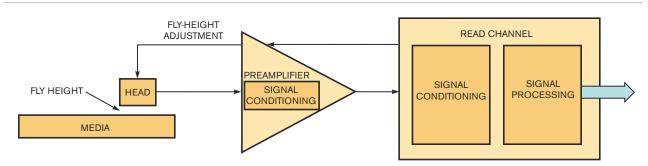

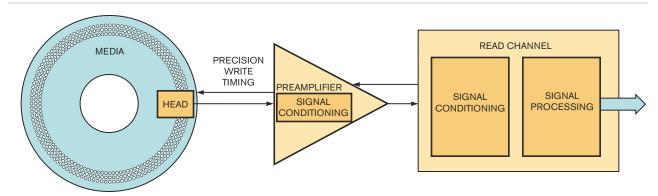

#### Preamplifier readchannel design addresses hard-drive goals

The hard-disk-drive industry is facing difficult challenges for increasing storage capacity and addressing cost, performance, power-consumption, and other important parameters. Jointly designing the media, head, flex, preamplifier, and read channel provides a good approach today and lays the foundation for future hard-drive generations.

by Harley Burger, LSI Corp

# Dilbert 10

- 1G-sample/sec. 12-bit ADC works in base stations and instrumentation

- 10 Touch controller lets you ignore extra touches

- 10 Power-converter IC targets dimmable LEDs

- 11 Quad power-converter control chip uses PMBus

- 12 RF vector signal generator combines high throughput, low phase noise

- 13 PIC32 expands connectivity support

- 13 DSP is energy-efficient

- 13 Channel-simulator mode takes only seconds to determine ultralow BER

- 14 Research Update: Coated optical fibers promise uniquely flexible PV cells: An old material for batteries turns out to have another nature

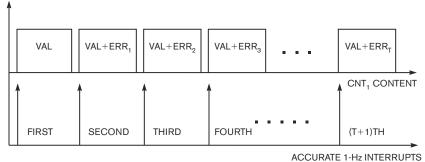

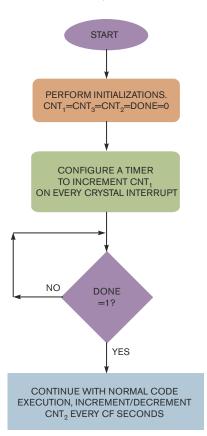

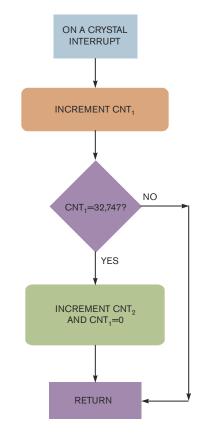

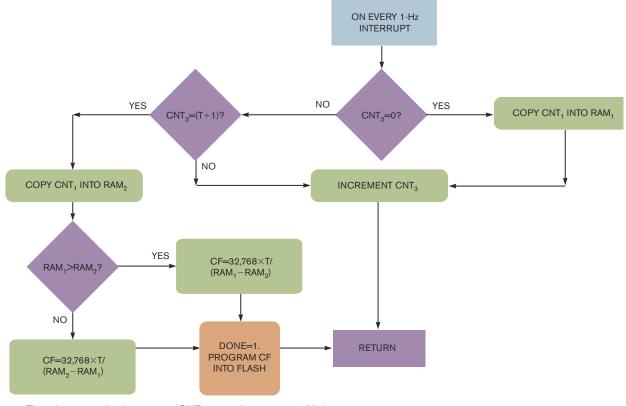

#### Taming inaccurate real-time clocks

An algorithm compensates of or oscillator inaccuracies and adjusts to changes in the environment and aging.

by Rufus Michael Gnana and Nazmul Hoda, Ittiam Systems

#### DESIGNIDEAS

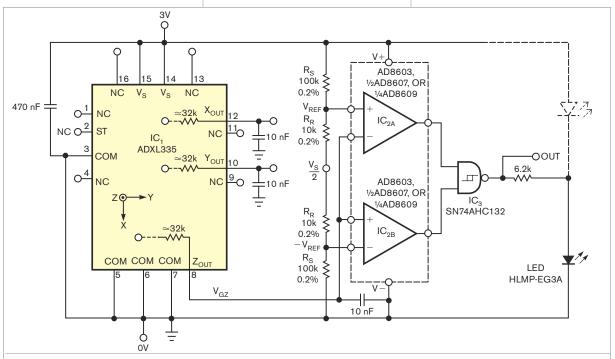

- 39 Precision tilt/fall detector consumes less than 1.5 mW

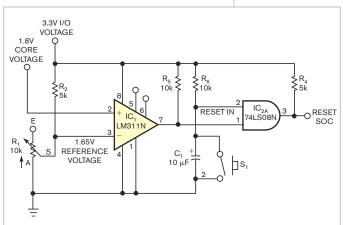

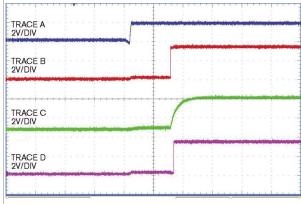

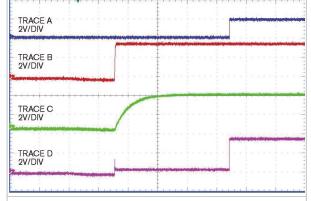

- 40 Reset an SOC only when power is ready

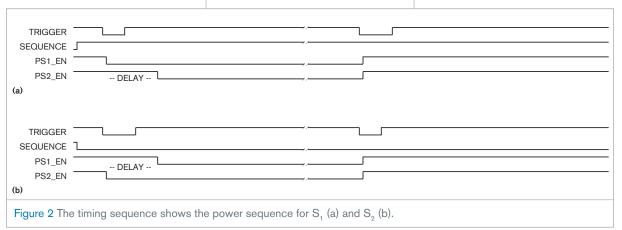

- 44 Circuit provides simpler power-supply-sequence testing

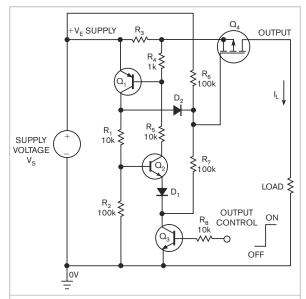

- 46 Inexpensive power switch includes submicrosecond circuit breaker

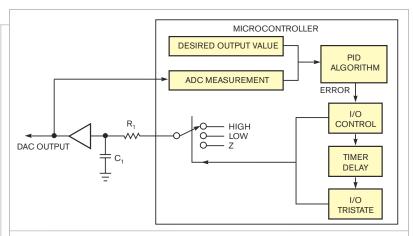

- 48 Create a DAC from a microcontroller's ADC

You can't get any cooler than Actel's IGLO0® FPGAs. And with the industry's widest range of packages—as small as 3x3 mm—you also can't get any smaller. IGLOO FPGAs are perfect for all of your portable, battery-powered applications, and anywhere you need to stretch your power budget to the maximum.

Designing products for the consumer, industrial, medical, automotive or communications markets? We've got you covered with a full range of solutions. As long as power matters, Actel FPGAs should be at the top of your list. Find out more at actel.com.

| Lowest Power |                |                | Low Power        |             |                  |                          |

|--------------|----------------|----------------|------------------|-------------|------------------|--------------------------|

|              | IGLOO          | •              |                  | Pro         | oASIC'I          | B                        |

| IGL00/e      | IGLOO<br>nano  | IGLOO PLUS     |                  | ProASIC3/E  | ProASIC3<br>nano | ProASIC3L                |

| Power        | Power and Size | Power and I/Os |                  | Performance | Cost             | Power and<br>Performance |

| •            | •              | •              | Low Power        | 0           | 0                | •                        |

| •            | •              | •              | Small Footprin   | t o         | •                | 0                        |

| •            | 0              | 0              | Logic Density    | •           | 0                | •                        |

| 0            | 0              | •              | I/O to Logic Rat | io 🔾        | 0                | 0                        |

| 0            | 0              | 0              | Speed            | •           | •                | •                        |

| 0            | 0              | 0              | Low Cost         |             | •                | •                        |

#### contents 12.3.09

#### **DEPARTMENTS & COLUMNS**

- 6 EDN.comment: Call me unconvinced by USB 3.0

- 16 Signal Integrity: Making Gaussian edges

- **Supply Chain:** Distributors respond to design trends; Digital-STB market still strong; Wisconsin signs electronics-take-back law

- 55 **Product Roundup:** Connectors, Computers and Peripherals

- 58 Tales from the Cube: Tanks a lot!

#### **EDN** online contents

www.edn.com

#### ONLINE ONLY

Check out these Web-exclusive articles:

#### New power-supply efficiency numbers herald a new era in power management

The EDN article "Industry standards lead push toward energy-efficient computing" discussed the new Platinum power requirements for high-efficiency ac/dc power supplies. But have we reached the point of diminishing returns by pushing efficiency requirements too high?

→www.edn.com/article/CA6707615

#### Secondary-side synchronous rectification boosts resonant converter efficiency

While secondary-side synchronous rectification in resonant half-bridge topology is not uncommon, its implementation has not been easy. A novel control scheme precisely turns on and off the secondary-side synchronous rectifier MOSFETs to achieve rectification that emulates a Schottky-diode rectifier, minimizing switching losses and optimizing conversion efficiency.

→ www.edn.com/article/CA6707473

Check out the full-strength online version of *EDN*'s annual Microprocessor Directory, which includes details on hundreds of processors and cores from more than 70 companies.

→www.edn.com/microdirectory

## INNO ATION

Nominations for the 20th annual Innovation Awards www.edn.com/innovation

EDN® (ISSN#0012-7515), (GST#123397457) is published biweekly, 24 times per year, by Reed Business Information, 8878 Barrons Blvd, Highlands Ranch, CO 80129-2345. Reed Business Information, a division of Reed Elsevier Inc, is located at 360 Park Avenue South, New York, NY 10010. John Poulin, CEO/CFO, RBI-US, Jeff DeBalko, President, Business Media; Jane Volland, Vice President, Finance. Periodicals postage paid at Littleton, CO 80126 and additional mailing offices. Circulation records are maintained at Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. Telephone (303) 470-4445. POSTMASTER: Send address changes to EDN®, PO Box 7500, Highlands Ranch, CO 80163-7500. EDN® copyright 2009 by Reed Elsevier Inc. Rates for nonqualified subscriptions, including all issues: US, \$179.99 one year; Canada, \$229.99 one year (includes 7% 6ST, GST#123397457); Mexico, \$229.99 one year; perceptiled, \$399.99 one year expertion, sucception, sucception of the properties of the prop

# Simpler Power Conversion

IR's AC-DC product portfolio offers simple, compact high density solutions tailored for energy-efficient power supplies.

#### µPFC™ PFC IC

| Part<br>Number     | Pckg.         | V <sub>cc</sub><br>(V) | Freq.<br>(kHz) | Gate<br>Drive<br>±(A) | V <sub>GATE</sub><br>Clamp<br>(V) | Current<br>Mode |

|--------------------|---------------|------------------------|----------------|-----------------------|-----------------------------------|-----------------|

| IR1150<br>(STR)PbF | SO-8<br>PDIP8 | 13-22                  | 50-200         | 1.5                   |                                   | CCM             |

#### SmartRectifier™ IC

|  | Part<br>Number                 | IR1166S<br>PbF | IR1167AS<br>PbF | IR1167BS<br>PbF | IR1168S<br>PbF |  |  |  |

|--|--------------------------------|----------------|-----------------|-----------------|----------------|--|--|--|

|  | Package                        | \$0-8          |                 |                 |                |  |  |  |

|  | V <sub>cc</sub> (V)            | 20             |                 |                 |                |  |  |  |

|  | V <sub>FET</sub> (V)           | <=200          |                 |                 |                |  |  |  |

|  | Sw Freq.<br>max (kHz)          |                | į               |                 |                |  |  |  |

|  | Gate Drive<br>±(A)             | +1/-4          | +2              | +1/-4           |                |  |  |  |

|  | V <sub>GATE</sub> Clamp<br>(V) | 10.7           | 10.7            | 14.5            | 10.7           |  |  |  |

|  | Min. On Time<br>(ns)           | P              | 750             |                 |                |  |  |  |

|  | Channel                        |                |                 |                 | 2              |  |  |  |

|  | RoHS                           | V              |                 | V               | ~              |  |  |  |

For more information call 1.800.981.8699 or visit

www.irf.com

International

Rectifier

THE POWER MANAGEMENT LEADER

#### BY BRIAN DIPERT, SENIOR TECHNICAL EDITOR

#### Call me unconvinced by USB 3.0

t September's IDF (Intel Developer Forum) in San Francisco, Steve Roux, senior strategic-business-development manager for USB (Universal Serial Bus) technologies at NEC Electronics, touted the benefits of Superspeed Version 3 of the USB specification, which is looming on the horizon. Judging from both company announcements and customer implementations, NEC is one of the notable Version 3 USB leaders in both stand-alone SOCs (systems on chips) and IP (intellectual-property)-core capability from its ASIC division.

Plenty of folks in the USB Pavilion at IDF were eager to chat about USB 3.0's 5-Gbps bandwidth potential and the extensive assortment of applications it will supposedly unleash.

Call me skeptical, at least in the short term. Consider first the viability of the 5-Gbps USB 3.0 performance claim. Anyone who has done USB 2.0 development and benchmarking will likely attest that real-life implementations don't come close to the technology's 480-Mbps potential. One reason for this disparity is that USB, unlike, say, IEEE-1394 FireWire, relies heavily on regular CPU intervention from transaction arbitration and scheduling standpoints. Other tasks can distract the CPU, making it less likely that the USB protocol's potential will translate into reality, even discounting the effects of multiple USB peripherals contending for common bus bandwidth. The other key reason for the disparity involves the applications themselves.

Mass-storage interfaces—as external hard-disk drives and as tethers to solid-state and magnetic storage within cameras and other devices—are obvious, popular uses for USB. A previous article compares eSATA (external

serial-advanced-technology ment), 400- and 800-Mbps IEEE-1394, and USB 2.0 (see "Interface overkill?" EDN, May 10, 2007, pg 48, www.edn. com/article/CA6437950). The article describes how USB 2.0 notably undershoots the performance potential of both hard-disk and solid-state drives. Other higher-speed interface alternatives, such as HDMI (high-definitionmultimedia interface) for digital videocameras, also exist for applications that demand higher speed than USB 2.0 can deliver. The cost constraints may preclude mass-market adoption of multi-interface designs, however. This same pricing pressure also means that USB 3.0 must achieve cost parity with USB 2.0 before the generational evolution will occur in earnest. At any rate, initial USB 2.0-versus-3.0 performance statistics were underwhelming, although more recent studies have garnered more promising results.

NEC's Roux also pitched such USB

3.0 applications as computer synchronization of PDAs (personal digital assistants), smartphones, portable multimedia devices, and the like, which currently operate at low speeds. In my experience, though, they're not notably faster over USB 2.0 than over USB 1.1, which suggests that the contentreconciliation routines running on both the computer and the tethered client—not the tether itself—are causing the bottleneck. As such, I doubt that USB 3.0 will make further discernible performance improvements. Speed aside, I wonder how much longer physical-wire tethering will be relevant. Don't consumers prefer reliable wireless tethering, either client to client or through a "cloud" intermediary server, and over Bluetooth, Wi-Fi, or a proprietary protocol?

Intel has remained mum on its USB 3.0-implementation schedule for its core-logic chip sets. As history shows, though, Intel's embrace of core logic is key to interface success. Rumors on the show floor at IDF suggested that Intel's adoption of USB 3.0 might slip to 2011 or later, and subsequent comments from both Intel's customers and its competitors bolster that contention. I also wonder whether Intel plans for even faster Light Peak technology, an optical-interconnect cable for PCs and mobile devices, to effectively obsolete USB 3.0.

Kudos to companies such as NEC for securing embryonic USB 3.0 design wins in both system boards and add-in cards. As with IEEE-1394, the IC sales will likely—at least at first—be profitable on a per-unit basis. As with IEEE-1394, however, they'll remain minuscule in volume unless manufacturers successfully address compelling application benefits and broad adoption.EDN

Contact me at bdipert@reedbusiness.com.

+ Read more at www.edn.com/blog/ 40000040/post/1560050356.html.

#### PRESIDENT, BUSINESS MEDIA, REED BUSINESS INFORMATION

Jeff DeBalko, jeff.debalko@reedbusiness.com 1-646-746-6573

#### PUBLISHER, EDN WORLDWIDE

Russell E Pratt, 1-781-734-8417; rpratt@reedbusiness.com

#### ASSOCIATE PUBLISHER, EDN WORLDWIDE

Judy Hayes, 1-925-736-7617; judy.hayes@reedbusiness.com

#### EDITOR-IN-CHIEF, EDN WORLDWIDE

Rick Nelson, 1-781-734-8418; rnelson@reedbusiness.com

#### **EXECUTIVE EDITOR**

Ron Wilson, 1-510-744-1263; ronald.wilson@reedbusiness.com

#### MANAGING EDITOR Amy Norcross

1-781-734-8436; fax: 1-720-356-9161;

amy.norcross@reedbusiness.com Contact for contributed technical articles

#### SENIOR ART DIRECTOR

Mike O'Leary 1-781-734-8307; fax: 1-303-265-3021; moleary@reedbusiness.com

#### ANALOG

Paul Rako, Technical Editor 1-408-745-1994; paul.rako@edn.com

#### MASS STORAGE, MULTIMEDIA, PCs, AND PERIPHERALS

Brian Dipert, Senior Technical Editor 1-916-760-0159; fax: 1-303-265-3187; bdiperl@edn.com

#### MICROPROCESSORS, DSPs, AND TOOLS

Robert Cravotta, Technical Editor 1-661-296-5096; fax: 1-303-265-3116; rcravotta@edn.com

#### **NEWS**

Suzanne Deffree, Managing Editor 1-631-266-3433; sdeffree@reedbusiness.com

#### POWER SOURCES, ONLINE INITIATIVES

Margery Conner, Technical Editor 1-805-461-8242; fax: 1-805-461-9640; mconner@reedbusiness.com

#### DESIGN IDEAS EDITOR

Martin Rowe, Senior Technical Editor, Test & Measurement World edndesianideas@reedbusiness.com

#### SENIOR ASSOCIATE EDITOR

Frances T Granville

1-781-734-8439; fax: 1-303-265-3131;

f.granville@reedbusiness.com

#### **EDITORIAL/WEB PRODUCTION**

Diane Malone, Manager

1-781-734-8445; fax: 1-303-265-3024 Steve Mahoney,

Production/Editorial Coordinator 1-781-734-8442; fax: 1-303-265-3198 Melissa Annand,

Web Operations Specialist 1-781-734-8443; fax: 1-303-265-3279 Adam Odoardi, Prepress Manager 1-781-734-8325; fax: 1-303-265-3042

#### CONSULTING EDITOR

Jim Williams, Staff Scientist, Linear Technology

#### CONTRIBUTING TECHNICAL EDITORS

Dan Strassberg, strassbergedn@att.net Nicholas Cravotta, editor@nicholascravotta.com

#### COLUMNISTS

Howard Johnson, PhD, Signal Consulting Bonnie Baker, Texas Instruments Pallab Chatterjee, SiliconMap

#### PRODUCTION

Dorothy Buchholz, Group Production Director 1-781-734-8329 Joshua S Levin-Epstein, Production Manager 1-781-734-8333; fax: 1-781-734-8096

#### EDN EUROPE

Graham Prophet, Editor, Reed Publishing +44 118 935 1650; gprophet@reedbusiness.com

#### EDN ASIA

Luke Rattigan, Chief Executive Officer luke.rattigan@rbi-asia.com Kirtimaya Varma, Editor-in-Chief kirti.varma@rbi-asia.com

#### **EDN CHINA**

William Zhang, Publisher and Editorial Director wmzhang@rbichina.com.cn Jeff Lu, Executive Editor jefflu@rbichina.com.cn

#### EDN JAPAN

Katsuya Watanabe, Publisher k.watanabe@reedbusiness.jp Ken Amemoto, Editor-in-Chief amemoto@reedbusiness.jp

EDN. 225 Wyman St, Waltham, MA 02451. www.edn.com. Phone 1-781-734-8000. Address changes or subscription inquiries: phone 1-800-446-6551; fax: 1-303-470-4280; subsmail@reedbusiness.com. For a free subscription, go to www.getfreemag.com/edn. Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. Include your mailing label.

# MAXIMUM)

#### RELIABILITY

In contact, stability and low-noise performance

Mill-Max Mfg. Corp. spring-loaded connectors provide superior reliability under the most rigorous environmental conditions, offering:

- Continuous, low-noise electrical connections.

- Spike-free stability to 50G shock and 10G vibration.

- Continued high performance through 1,000,000+ cycles.

- Low- and high-profile surface-mount styles.

- 45 discrete designs for customer-specific assemblies.

- 6 families of single and double strip assemblies.

- The shortest production lead times in the industry.

**SLC Connector Assemblies**

Stay in contact with Mill-Max spring-loaded connectors.

To view our Design Guide, new product offerings and request a datasheet with free samples, visit

www.mill-max.com/EDN596

# MEET THE GUY that ELIMINATED HIS TEAM'S MANUFACTURING VARIABILITY ISSUES.

FIX YOUR MANUFACTURING VARIABILITY PROBLEMS AND YOUR REPUTATION WILL PRECEDE YOU. If you're designing chips for high functionality, high speed and lower power consumption at the most advanced process nodes, you've got variability issues. We have the solution that will increase your yield, performance and prestige by a wide margin. | Get more information at mentor.com/solutions/manufacturing-variability.

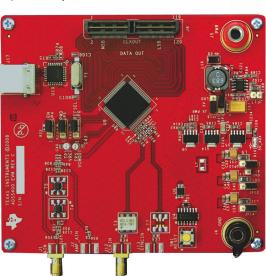

#### 1G-sample/sec, 12-bit ADC works in base stations and instrumentation

argeting applications in wireless-communications, defense, and test-and-measurement equipment, Texas Instruments recently announced the 12-bit, 1G-sample/ sec ADS5400 ADC with 2.1-GHz input bandwidth. You can adjust the device's gain, offset, and phase to interleave two or more ADCs to create a multigigabit-sample/second digitizer or to balance two ADCs in an I/Q (in-phase/ quadrature) wireless receiver. You can select between single- or dual-bus DDR LVDS (lowvoltage-differential-signaling) outputs.

The device offers an SNR (signal-to-noise ratio) of 59 dBFS (decibels below full-scale) and 75 dBc (decibels referenced to the carrier) SFDR (spurious-free dynamic range) in the first Nyquist frequency range. For intermediate frequencies beyond 1000 MHz, the SNR is 58

dBFS, and the SFDR is 70 dBc. The device has buffered analog inputs and an internal sampleand-hold circuit.

The ADS5400 comes in a 100-pin  $16 \times 16$ mm TQFP package, operates over -40 to 85°C, and sells for \$775 (1000). Samples and an evaluation board that is compatible with Tl's TSW1200EVM digital-capture card are available now.-by Paul Rako

▶Texas Instruments, www.ti.com.

- FEEDBACK LOOP "Will the machines eventually take over? Nope. **People have** wants; machines want nothina."

-Hardware architect David Wyland, in EDN's Feedback Loop, at www.edn.com/ article/CA6694951. Add your comments.

The evaluation board for TI's ADS5400 ADC allows you to assess the unit's performance.

tekmicro.com) uses eight ADS5400 chips to provide fast digitization for applications such as beam forming, radar, military countermeasures, and wireless communications.

#### Touch controller lets you ignore extra touches

he mXT224 maXTouch touchscreen controller from Atmel combines the company's mutual capacitive sensors, a charge-transfer method of signal acquisition, and an Xmega microcontroller with bundled software to provide processing for handling an unlimited number of touches on a touchscreen. Mutual capacitance sensors avoid the ambiguity of multitouch positions that self-capacitance sensors experience by forming independent sensing nodes at each intersection of rows and columns over the display surface. At each intersection, the sensor emits a fixed number

of mutually coupled voltage pulses along each set of row and column lines; this action causes a known current flow in the selected pair of lines. This sensing approach yields an SNR (signal-to-noise ratio) of 80-to-1, which enables the system to unambiguously manage multiple simultaneous touches and more accurately sense weak and adjacent signals with a refresh rate as high as 250 Hz.

The integrated processor and bundled software provide additional processing for advanced noise-suppression algorithms for even more immunity to couplednoise issues. Altogether, this approach enables the system to better identify and ignore unintended touches, such as when a user's hand overlaps the edge of the display while holding it or rests on the writing surface while using a stylus to provide a signature.

The mXT224 supports 224 X/Y sensing nodes and consumes less than 5 mW. It provides enough precision to support zoom, pinching, rotate, handwriting, and shape-recognition capability in screens as large as 10 in. You can use multiple mXT224 controllers together to provide smaller interspatial distances between touches on larger screens. The integrated single-cycle RISC AVR core includes two on-chip DSP engines that process the X and Y positions on the touchscreen. The system provides 16 X drive lines and 14 Y sense lines; you can reconfigure as many as four of the Y sense lines as X drive lines for a 20×10-line configuration.

The mXT224 is available now in a 5×5-mm BGA package and sells for \$4.75 (1 million). The EVK-mXT224A evaluation kit, including a 4.3in. touchscreen and a PCB (printed-circuit board) that connects to a PC over USB, is available now for \$400. For more on these products, go to www.edn. com/article/CA6699917.

-by Robert Cravotta

>Atmel, www.atmel.com.

# maXTouchTM

The mXT224 encompasses the front-end signal-acquisition and postprocessing algorithms for multitouch systems in a single package.

#### **DILBERT By Scott Adams**

#### POWER-CONVERTER **ICTARGETS DIMMABLE LEDs**

The large installed base of dimmable-lighting switches dictates that most new lighting technologies, including LED lights, should support dimming, and the myriad disparate specifications for dimming switches require these lights to meet a wide range of char-

The iW3610 provides ac/dc-power control for LED lights.

Meeting both of those requirements, iWatt's new iW3610 ac/dc digital-power controller for dimmable

LEDs includes intelligent wall-dimmer detection for both leading- and trailing-edge dimmers. It also detects an unsupported dimmer and turns off the light rather than self-destructing. The IC supports dimming from 2 to 100% and has an optimized dimming frequency of 900 Hz, so there is no visible flickering over the entire range.

The 3610 uses primaryside regulation, eliminating the need for an optocoupler and sense resistor for dimmable LED lights of 40W or lower wattage. Another version, the iW3620, is similar to the 3610 but does not support dimming.

The 3620 has an internal switching frequency of 130 kHz and sells for 38 cents (1000); the 3610 sells for 98 cents (1000). For more, go to www.edn.com/ article/CA6706827.

-by Margery Conner iWatt, www.iwatt.com.

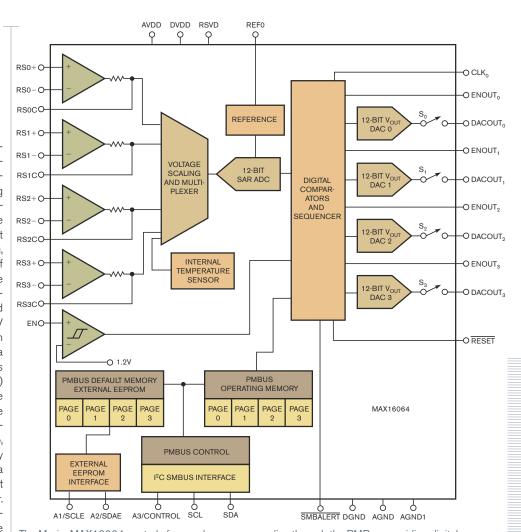

#### Quad powerconvertercontrol chip uses PMBus

axim's new MAX-16064 monitoringand-control chip supervises four analog switching power converters. You communicate with the IC over the PMBus (power-management bus) to perform sequencing, monitoring, and margining of analog power supplies. The device controls output voltages with ±0.3% accuracy, and you can power it from 3 to 3.3V rails. Other features include an internal temperature sensor, a reset output, and an SMBus (system-management-bus) alert output. You can also store the chip's user-programmable registers in a low-cost external EEPROM. At power-up, the MAX16064 automatically retrieves the EEPROM data and loads the registers without requiring a system controller. Storing fault data in the external EEPROM also eases the identification and debugging of failures. The part features master/slave-clock options so that you can maintain accurate timing references across multiple devices.

Applications include highreliability systems, such as servers, storage, base stations, routers, and networking equipment with multiple power supplies. The unit includes a GUI (graphical user interface) for implementing a digitally programmable power supply. The MAX16064 comes in a  $6\times6$ mm, 36-pin TQFN package; operates in the -40 to  $+85^{\circ}$ C range; and sells for \$6.34 (1000).-by Paul Rako

**►Maxim Integrated**

Products, www.maxim-ic.com.

The Maxim MAX16064 controls four analog power supplies through the PMBus, providing digitalpower benefits to analog-power systems.

The Maxim MAX16064 digital controller chip adds the benefits of digital power to analog converters.

#### RF vector signal generator combines high throughput, low phase noise

**✓** eithley Instruments

has upgraded its RF vector signal generator line with new capabilities that reduce signal-generation times and enhance signal quality. The instrument, which provides signal-generationbandwidth options to 80 MHz and frequency ranges from 10 MHz to either 4 or 6 GHz, sells for \$17,850 and \$23,460, respectively.

A patent-pending technique, which ensures fast settling of phase-locked-loop synthesizers, allows the instrument to tune in 300  $\mu sec$  or less to new frequencies in a DUT's (device under test's) operating band; competitive products typically require 600 µsec or longer. The unit allows switching of amplitudes in as little as 150 µsec compared with more than 500 µsec for competitive generators. This fast settling reduces the time required to test devices over their full power-handling range.

Because testing of devices that operate on multiple standards requires rapid switching among numerous complex signals, the unit's onboard arbitrary-waveform generator includes a 100M-sample memory that can hold large individual waveforms or multiple smaller ones. This deep memory combines with the instrument's speed-optimized list mode and a sequencer operating mode to support switching from one waveform to another within a single processor-clock cycle-even with waveforms that conform to different standards and employ different modulation schemes.

A direct link from the instrument's digital-signal-processing-circuit block to an external PC through a USB (Universal Serial Bus) 2.0 maximizes operating speed. In this highspeed desktop-control-panel operating mode, the external PC controls the instrument and acts as if it were the instrument's onboard-processor controller. This mode supports 100-Mbps transfers of signal files from the PC directly into the instrument's arbitrary-waveform memory and enables faster, simpler downloading of large files, such as streaming-videotest-signal files, signal files modified by channel models, and radar-profile files. With its high download speed and the manufacturer's application software, the unit can quickly perform dynamic-frequencyselection-conformance testing on WLAN (wireless localarea-network) access points, verifying a device's compliance with government and industry standards, which ensure that these transmissions do not interfere with radar signals, such as those for weather monitoring and air-traffic control. You can create wave-

Re unit allows switching of amplitudes in as little as 150 μsec.

form files offline and download them into the instrument's arbitrary-waveform memory using a USB memory stick or the unit's IEEE 488 or LAN interfaces. This transfer flexibility is convenient for those who create signal files with third-party tools, such as The MathWorks' (www.mathworks. com) Matlab.

Unlike competitive signal generators, which typically maximize either throughput or signal purity, the 2920A's design allows you to optimize whichever performance aspect is more critical in your application: High signal purity is essential when you create complex signals that conform to many wireless-communication standards. To ensure the quality of these signals, the 2920A-UPN (ultralow-phase-noise) option provides noise levels of less than or equal to -135 dBc/Hz

at a 300-kHz offset from a 2-GHz carrier. This performance allows the generation of wideband-code-division-multipleaccess signals with EVMs (error-vector magnitudes) of less than 0.85% of the signal amplitude. This option also permits the 2920A to generate 5.8-GHz, 40-MHz-bandwidth IEEE 802.11n WLAN signals with an EVM of less than -43dB and WiMax signals with a residual relative constellation error of less than or equal to -43 dB. In addition, when you use the UPN option, the 2920A provides tuning as fast as 750 µsec.

The 2920A's wide signal range suits it to testing a broad spectrum of receivers and components. The 2920A-LAR (low-amplitude-range) option extends that range to allow the generator to output signals of -130 to +13 dBm. The unit's accuracy, repeatability, and stability allow you to set narrow limit bands in your test protocols. Absolute amplitude accuracy to 3 GHz is  $\pm 0.6$  dB maximum, or ±0.3 dB typical, from -110 to +13 dBm. Relative amplitude accuracy, or linearity, is  $\pm 0.05$  dB, and amplitude repeatability is ±0.05dB.

With the manufacturer's SignalMeister RF-communications-test-tool-kit software and Model 2820A vector signal analyzer, it can easily generate and analyze MIMO (multiple-input/multiple-output) signals. With signal personalities that the software provides, the 2920A can not only generate pure signals but also replicate impaired signals for in-depth receiver characterization. For more on this product, go to www.edn.com/ article/CA6700416.

-by Dan Strassberg Keithley Instruments Inc, www.keithlev.com/products.

The cost-effective 2920A RF signal generator does not force trade-offs between accuracy for component evaluation in R&D and speed for production test.

#### PIC32 expands connectivity support

icrochip Technology's PIC32MX5/6/7family chips expand the connectivity support of PIC32 processors to cover 10/100-Mbps Ethernet; CAN (controller-area-network) 2.0b; and USB (Universal Serial Bus) host, device, and OTG (On-The-Go) peripherals. The company offers free TCP/IP (Transmission Control Protocol/Internet Protocol) and USB host- and device-software stacks, including source code, for these families. The 100-Mbps Ethernet MAC (media-access controller) uses an RMII/MII (reduced media-independent interface/ media-independent interface) and includes a unique factorypreprogrammed Ethernet MAC address.

The CAN2.0b controllers use system RAM for storing as many as 1024 messages in 32 buffers with as many as 32 filters and four filter masks. Additional available software includes support for AES (Advanced Encryption Standard), multiple file systems, graphics, and audio libraries.

Microchip's PIC32MX5/6/7 ICs cover Ethernet, CAN, and USB connectivity.

The 80-MHz, 32-bit processors include as much as 128 kbytes of RAM, six UARTs (universal-asynchronous-transmitter/receiver) interfaces, five I<sup>2</sup>C (inter-integrated-circuit) interfaces, and four SPI (serialperipheral-interface) ports.

The three new PIC32-MX5/6/7 families are available for sampling, and prices range from \$4.73 to \$6.55 (10,000). Package options include 100-pin TQFP and BGA packages and 64-pin TQFP and QFN packages.

The PIC32MX5/6/7 families are pin-compatible with the PIC32 and 16-bit PIC24F USB devices. Starter kits include the \$72 DM320004 PIC32 Ethernet starter kit and the \$55 DM320003-2 PIC32 USB II starter kit. Owners of the DM240001 Explorer 16 development board can purchase the \$25 MJA320003 plug-in module for development with the new PIC32MX5/6/7 families.-by Robert Cravotta

>Microchip, www.microchip.

#### **DSPISENERGY-EFFICIENCT** Texas Instruments' new

six-core TMS320C6472 DSP boasts a 3.68W power-use sweet spot when operating all six cores at 500 MHz with 80% usage. The cores support 625- and 700-MHz operation with a trade-off of energy efficiency at the 500-MHz operation point. The device includes 4.8 Mbytes of L1 and L2 memory partitioned so that each core has a dedicated portion of the memory as well as access to 768 kbytes of shared L2 program/data memory. The sharedmemory controller provides no hardware-based coherency support, so applications requiring coherency require software management.

Connectivity peripherals include GbE (gigabit Ethernet), Serial RapidIO, DDR2, a telecom-serialinterface port, a host-port interface, Utopia, I2C (inter-integrated circuit), and GPIO (general-purpose input/output). These devices target high-end industrial, test-and-measurement, communication, medicalimaging, high-end imaging and video, and bladeserver designs.

The TMS320C6472 is available now at prices starting at \$140 (1000). The TMDXEVM6472 evaluation module is available for \$349. For more on this product, go to www.edn. com/article/CA6705855.

-by Robert Cravotta Texas Instruments, www. ti.com.

#### Channel-simulator mode takes only seconds to determine ultralow BER

gilent Technologies has introduced a statistical mode for its signal-integrity channel-simulator tool. The mode, part of Agilent's ADS (Advanced Design System) 2009 Update 1, supports the design and verification of today's high-speed, chip-to-chip data links in most consumer and enterprise digital products-from laptop computers and data-center servers to telecommunication switching centers and Internet routers.

The simulator eliminates the need for costly and time-consuming prototype iterations and allows designers to perform simulations using circuit-level models that they can then verify against measured data and EM (electromagnetic) simulation of the layout. ADS 2009 Update 1 also features a BER contour and bathtub display, equalizer support with automatic tap optimization, an eye-mask utility with automatic violation checking, the ability to check crosstalk with aggressors at different data rates, a memory-bus-compliance tool for the DDR3 standard, ECL (emittercoupled-logic) models that comply with the IBIS (input/output-buffer-information specification), and a time-domain-reflectometry tool.

The Agilent ADS 2009 Update 1 is now available. The base price for the new channel-simulator mode is \$28,000. For more information on this product, go to www.edn.com/article/ CA6702836.-by Rick Nelson

>Agilent Technologies, www.agilent.com/ find/signal-integrity.

## pulse

#### **M RESEARCH UPDATE**

BY RON WILSON

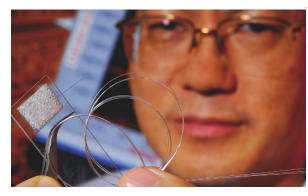

## Coated optical fibers promise uniquely flexible PV cells

ne of the big practical issues with silicon solar cells is where to put them. Their conversion surface is also their collecting surface, so you end up with a huge flat panel facing the sun. This scenario limits the configura-

tions in which designers can deploy the panels.

Now, researchers at the Georgia Institute of Technology have found an alternative. By coating an optical fiber with a nanostructured, dye-sensitized PV (photovoltaic) coat-

Zhong Lin Wang holds a prototype 3-D solar cell that could allow designers to locate PV systems away from rooftops.

ing, the researchers have created a device in which conversion takes place over a dense nanowire fur all along the surface of the fiber, giving a conversion surface far greater than the collecting surface's area.

To form the structure, Zhong Lin Wang, Georgia Tech Regents Professor of materials science and engineering, and his team first strip the cladding from a communications-grade quartz fiber. They then apply a conductive coating and a seed layer of zinc oxide to the wall of the fiber. They grow zinc-oxide nanowires on the prepared surface with established techniques, ending up with a fiber surrounded by a fur of nanowires with an enormous total

surface area. The researchers then coat the nanowires with dye-sensitized PV material, immerse the fiber in liquid electrolyte to collect the current from the PV reaction, and point the end of the fiber at the sun or focus lighting into the fiber with external optics.

Wang says the structure's high saturation intensity makes optical concentration productive. Once light enters the unclad fiber, some light passes through the wall into the nanowires at each reflection along the inside wall and thence into the huge area of PV material. Wang and his team have demonstrated 20cm fibers and 3.3% efficiency: switching to titanium oxide and improving charge collection could increase conversion efficiency to perhaps 8%.

**⊳Georgia Tech**, www.gatech. edu.

#### AN OLD MATERIAL FOR BATTERIES TURNS OUT TO HAVE ANOTHER NATURE

A team from Johns Hopkins University recently found that a nonsemiconductor that has long found use as a conductor turns out also to be, in a different orientation, an insulator, with properties useful in constructing MOSFETs (Reference 1). The material, solution-deposited beta alumina, forms when aluminum oxide from solution forms solid layers of crystals.

Howard E Katz, professor of materials science and engineering at Johns Hopkins, explains that, because the material forms from solution, it is easy to lay down in arbitrary patterns. Heating the deposited material to 400°C causes the formation of sodium beta alumina, a hard, transparent film with the mobile sodium ions still trapped between planes of aluminum oxide. These characteristics make the film compatible with applications on the surface of flat-panel displays, for example.

The familiar conductor conducts only when parallel to the plane of the film. Perpendicular to this plane, the material acts as an insulator. Further, if you apply a voltage perpendicular to the film, the voltage causes the ions trapped between layers of alumina to shift, polarizing the material. This polarization results in a dielectric constant (k) of 200-about 50 times that of silicon dioxide.

The team has employed sodium beta-alumina films to fabricate FETs on a variety of semiconductor substrates, including silicon and indiumzinc oxide. The transistors display low-voltage operation, the ability to operate into low-megahertz frequencies, transparency, and flexibility.

Johns Hopkins, www.jhu.edu.

#### REFERENCE

1 Pal, Bhola N, Bal Mukund Dhar, Kevin C See, and Howard E Katz,

Howard E Katz adjusts probes for testing electronic devices (photo courtesy Will Kirk, Homewoodphoto.jhu.edu).

"Solution-deposited sodium betaalumina gate dielectrics for low-voltage and transparent field-effect transistors," *Nature Materials*, November 2009, Volume 8, No. 11, pg 898, www. nature.com/nmat/journal/v8/n11/ abs/nmat2560.html.

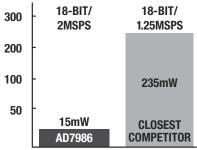

# When high performance and low power make the design, ADI converters make the difference. AD7986: True 18-Bit Performance at 2 MSPS Output O

Power dissipation at full performance

### 15 mW, 18-bit, 2 MSPS, ADC delivers industry-leading performance without the heat.

Mainement 159 (15)

Designers of high channel count, high precision data acquisition systems inevitably face the challenges of minimizing both power consumption and design footprint. Achieving maximum system throughput under these circumstances required either multiplexed high speed resolution ADCs, which generate more heat, or multiple low speed resolution ADCs, which take up extra board space. With power dissipation levels nearly  $15\times$  lower than the competition and a smaller footprint, the AD7986 eliminates the need for such trade-offs. And you'll find many more industry-leading examples like this one throughout our high precision SAR converter portfolio at www.analog.com/PulSAR.

| Part Number | Speed<br>(MSPS) | Resolution<br>(Bits) | Features                     | Power Dissipation (mW) |

|-------------|-----------------|----------------------|------------------------------|------------------------|

| AD7986      | 2               | 18                   | 97 dB SNR, $\pm 2.5$ LSB INL | 15                     |

| AD7985      | 2.5             | 16                   | 90 dB SNR, $\pm 1.5$ LSB INL | 15.5                   |

| AD7944      | 2.5             | 14                   | 84.5 dB SNR, ±1 LSB INL      | 15.5                   |

All products available in 20-lead LFCSP package.

#### BY HOWARD JOHNSON, PhD

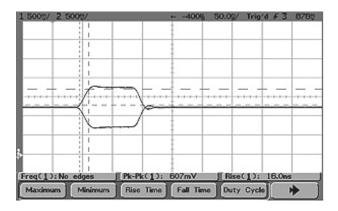

#### Making Gaussian edges

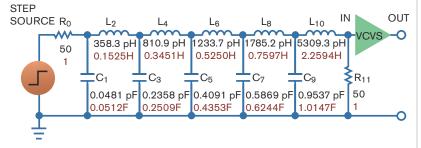

he analog-filter network in **Figure 1** converts each input step into a smooth, Gaussian-shaped rising and falling edge. When simulating high-speed systems in Spice, you can use this filter network instead of PWL (piecewise-linear) edge-shaping because it better represents how real signals behave. The analog filter comes from Anatol I Zverev's *Handbook of Filter Synthesis*, a classic compendium of passive-filter designs

(Reference 1). The book lists circuits for implementing many types of filters, including approximations of the Gaussian filter. The approximation is not exact because an actual, perfect, Gaussian response would have an infinitely long precursor. The author derives the filter approximation as a 10th-order truncation of the Taylor series expansion for the square of a perfect Gaussian-network function. He assumes ideal components with no significant parasitic effects.

Zverev specifies a current-source driver for the filter and shunts the current source with resistor  $R_0$ . Figure 1 drives the circuit differently. It uses

# The analog-filter network better represents how real signals behave.

a voltage source that connects in series with  $R_0$ . Either approach produces a driver with an output impedance of  $50\Omega$ . Using a voltage source ensures that the circuit's output amplitude will be precisely half the voltage source's amplitude.

The circuit values in black in Figure 1 differ from the original circuit values in Zverev's book, which the

NOTE: THE COMPONENT VALUES IN RED ARE THOSE IN THE ORIGINAL CIRCUIT IN REFERENCE 1.

Figure 1 This 10-pole network approximates a Gaussian filter with a 10 to 90% rise and fall time of 100 psec.

figure shows in red. The author designed his circuit for an impedance level of  $1\Omega$ . Figure 1 scales that impedance to a more commonly accepted value of  $50\Omega$ . It does so by multiplying the book's resistances and inductances by 50 and dividing the capacitances by 50.

The 3-dB frequency of Zverev's original circuit equals 1 rad/sec, or 0.159154 Hz, making a 10 to 90% rise/fall time of 2.12773 seconds. Figure 1 scales the filter to a 100-psec rise time by multiplying all the capacitor and inductor values by the ratio  $\tau/(2.12773)$ , where  $\tau$  is the desired rise time. This time-scaling operation leaves the resistor values unchanged.

The combination of impedance-and time-scaling operations in Figure 1 produces a  $50\Omega$  filter with a 100-psec rise and fall time. The filter tracks true Gaussian behavior down to -40 dB within  $\pm 1$  dB, with a slope of 60 dB per octave after that (Figure 2, which is available in the Web version of this article at www.edn.com/091203hj). The nominal delay of the 10-pole model, from zero to 50%, is 1.485 times the 10 to 90% rise time. Remember this delay when making your timing calculations. You'll see it in the Spice model.

Always follow Zverev's filter with a buffer. In Spice terminology, a perfect buffer is a VCVS (voltage-controlled voltage source). The buffer prevents any attached loads from changing the filter's performance. Connect your driver's source-resistance and package models to the output of the buffer.EDN

#### REFERENCE

Zverev, Anatol I, Handbook of Filter Synthesis, John Wiley & Sons, New York, 1967.

Howard Johnson, PhD, of Signal Consulting, frequently conducts technical workshops for digital engineers at Oxford University and other sites worldwide. Visit his Web site at www.sigcon.com or e-mail him at howie03@sigcon.com.

# Next generation 3D electromagnetic simulation

The best available tool for 3D EM simulation has evolved into version 2010. With a user friendly interface, easy data exchange to and from other software tools, a choice of first class solvers and world class post-processing tools, you can leverage the latest developments in 3D electromagnetics to bring designs to market faster and with lower risk.

Choose CST STUDIO SUITE 2010 – complete technology for 3D EM.

CHANGING THE STANDARDS

## The world standard.

TDS3000C Series 100 to 500 MHz

DPO70000B/DSA70000B Series 4 to 20 GHz

TDS1000B/TDS2000B Series 40 to 200 MHz

DPO7000 Series 500 MHz to 3.5 GHz

MSO2000/DPO2000 Series 100 to 200 MHz

DPO3000 Series 100 to 500 MHz

DSA8200 Series DC to 70+ GHz

MSO4000/DPO4000 Series 350 MHz to 1 GHz

## 8 out of 10 engineers the world over rely on Tektronix oscilloscopes to help them meet their design goals. So can you.

The vast majority of engineers depend on the industry-leading performance, precision, flexibility, ease-of-use and reliability of Tektronix oscilloscopes, software applications and accessories. In short, they set the standard by which all others are judged. Our broad portfolio includes everything from complete debug and analysis to the most advanced acquisition engines. In fact, Tektronix has remained an innovator in test and measurement for over 60 years. So rely on a Tektronix scope, and the experts standing behind it, to help you take on the world.

The best scopes on the planet.

Download the product catalog at: www.tektronix.com/catalog

THE CONTINUAL EVOLUTION OF MICROPROCESSORS AND A WIDENING BASE OF DEVELOPERS WHO NEED DIGITAL SIGNAL-PROCESSING TECHNOLOGY ARE CAUSING A TREND AWAY FROM STAND-ALONE DSPs.

## The evolving landscape of DIGITAL SIGNAL PROCESSING

BY ROBERT CRAVOTTA • TECHNICAL EDITOR

s the stand-alone DSP a dying breed? It may not exactly be dying, but the DSP is not front and center as it used to be. In 2006, EDN changed the name of its annual DSP Directory to the Digital Signal-Processing Directory (Reference 1). This subtle change recognizes that digital-processing options have commercially expanded beyond just software-programmableprocessor devices and core offerings to include other options, such as programmable fabrics, IP (intellectual-property) blocks, and mixed-processing SOCs (systems on chips). These processing options complement as well as compete with each other because each faces a different set of constraints (Reference 2).

Signal processing involves mathematical manipulation for transforming—using filtering, Fourier transform, compression, decompression, synthesizing, recognizing, enhancing, encoding, decoding, and other methods—a set of data or a stream

of signals. The continual advancement of microprocessors and growing base of developers who need this technology are leading the trend away from stand-alone

The war between FPGAs (field-pro-

grammable gate arrays) and DSPs has died down over the past few years. Both camps have realized that they best serve different types of problems and that it is common for an FPGA and a processor to be operating side by side in one design. FPGAs can leverage arbitrarily wide signal-processing algorithms acting as hardware-acceleration blocks. This ability gives them an advantage over DSPs when the signal-processing algorithm is sufficiently wide enough that it can efficiently use more than the available processing units in the DSP. However, working with FPGAs is more complex in part because of their hardware-design flow. For example, Xilinx is focusing on making the FPGA easier to use, according to Tom Hill, senior marketing manager for DSP solutions at the company. Xilinx accomplishes this task by abstracting the complexity of the design process, including accommodating a C-design flow and C-synthesis tools for hardware and software partitioning.

As microprocessors continue to benefit from Moore's Law, they can incorporate multipliers and specialized circuits, including specialized bus architectures and memory hierarchies, to improve their computational performance. Some of today's microprocessors deliver good computational performance, low cost, and high energy efficiency. If these parameters are good enough, these microprocessors let designers add and accommodate signal processing in a design within a single chip. These processors do not necessarily deliver the best-inclass processing performance, cost, and energy efficiency, but they offer other system-level advantages, including billof-materials cost savings or a familiar design flow, and can thus be better choices than stand-alone DSPs.

#### WHAT'S IN A NAME?

As signal processing expands into more applications, ease of use becomes a critical concern despite the fact that designers historically often associate the term "DSP" with complexity. Early DSPs involved architectures that focused on extracting the maximum processing performance rather than on the ease of transforming mathematical algorithms into silicon and software implementations. As these processors evolved and were able to use more transistors with each new generation, they could better accommodate the transformation in various ways. Processors that allow programming in C, for example, help with this transformation.

Consider how Texas Instruments identifies its TMS320C2000 platform. The company once referred to these devices as DSPs with controller capabilities. A few years ago, however, these processors became known as DSCs (digital signal controllers). The company recently removed the C2000 from the 2009 EDN DSP Directory and now refers to it as a real-time microcontroller, even though the underlying architecture has not changed. The explicit focus has changed, however, to making the surrounding development-support environment more comfortable to microcontroller developers.

#### AT A GLANCE

- Embedded signal processing is quietly appearing within more processing options and application designs.

- Silicon providers are building application-targeted products to support the casual use of signal processing.

- Each skill for developing signal processing works at different levels of abstraction and with different natural data forms.

You may think that manufacturers taking this tack are being disingenuous, but keep in mind that many processor offerings place the focus on the target application and only imply the signal-processing capability. Examples include the Analog Devices Blackfin audio, video, and communications processors; ARM processors with Neon or accelerated multimedia IP; Freescale Power Architecture with Altivec extensions: Infineon TriCore automotive and industrial processors; Intel Pentiums with SSE (streaming single-instruction/ multiple-data extensions); Microchip DSPic motor-control and power-conversion DSCs; NXP CoolFlux processors; Tensilica Xtensa audio and video engines; and Texas Instruments DaVinci and OMAP (open-multimedia-applications-platform) processors.

Each of these processors incorporates signal-processing architectural features from which their target application benefits. Application-specific algorithms or signal-processing libraries are available with many of these devices not only to improve time to market but also to enable developers to add capabilities to their designs without becoming experts about the new functions. Processor vendors are bundling silicon and software to simplify audio and video processing and other applications.

#### **CASUAL-USER ADOPTION**

Identifying processors by their target application reflects the trend for silicon providers to offer application-targeted products or implemented reference designs that comprise not only the hardware but also the appropriate software components that work with that hardware. Developers can buy or license targeted implementations for a growing array of signal-processing functions, such as

compression, audio, and video encoding and decoding. These developers' focus is shifting from how to build core functions to whether an implementation meets performance, price, energy, time-to-market, and integration goals. Algorithm and system providers who can find the balance between delivering processing performance, energy efficiency, algorithm flexibility, and robust system integration should stand out in this increasingly competitive area.

The signal-processing nature of the bundled software in these offerings is sometimes less obvious. For example, touch sensing is such a popular capability that many processor vendors this year rolled out or updated touch-sensing support for their devices. These packages include processor targets with software and demonstration kits to ease the learning curve for developers trying to use the technology. The developer targets an API (application-programming interface), which hides from the developer much of the complexity of accessing the touch sensors. Managing and interpreting the touch-sensor inputs usually require significant amounts of signal processing, especially with the multitouch products, to filter and calibrate the sensor to deliver a consistent and reliable input source. Processor vendors are building their own in-house touch-sensing expertise and abstracting the complexity from the end developer. This step allows the developer to focus on higher-level interpretations of the touch inputs, such as recognizing command gestures.

This industrywide trend is moving digital signal processing to the level of a deeply embedded technology in which a growing percentage of developers are not concerned with the implementation details of "commodity" signal processing. This trend enables silicon providers to reach the larger set of developers who are not signal-processing experts without encumbering them with the learning curve of implementing these algorithms from scratch. It also makes irrelevant the dirty secret of the most optimized signal-processing implementations—that the software is often hand-optimized assembly or C code with heavy usage of compiler intrinsics to squeeze the best performance from the underlying hardware. Developers can continue to use the familiar C-code design flow for their value-added part of the system without

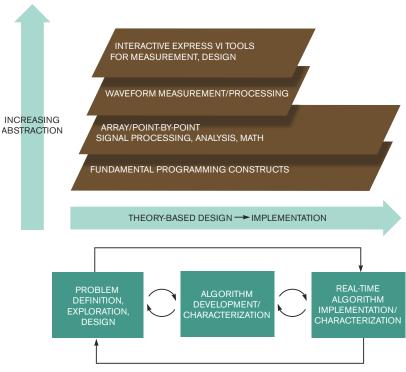

Figure 1 The stacked blocks represent categories of functions, based on the level of abstraction of their programming interface and number of encapsulated functions (courtesy National Instruments).

concern for implementing the coding of the licensed, timing-critical "heavy lifting." It also provides the groundwork for certifying the algorithmic implementations as the silicon providers continue to build their core group expertise.

This emerging abstraction layer helps support the exploding increase in the number of casual users who are adopting signal processing. However, it represents another layer of complexity for the silicon providers' development support because the power and intermediate users of these processors still need visibility down to the metal to support their innovation explorations. Piergiovanni Bazzana, an application developer at Atmel, describes two of the company's customers that wanted to employ the same Atmel dual-core microcontroller/DSP processor for the same type of end product. The smaller company wanted to use a single graphical programming tool to develop both the microcontroller and DSP cores because the company had fewer resources to dedicate to the project and was interested in implementing compliant standard algorithms. The

# CADENCE OrCAD RELEASE 16.3 YOUR WINDOW TO THE FUTURE

#### **New Cadence OrCAD Release 16.3**

From front-end design creation with Cadence® OrCAD® Capture and OrCAD Capture CIS to circuit simulation and analysis with Cadence PSpice® A/D and PSpice Advanced Analysis to back-end layout with Cadence OrCAD PCB Editor, the OrCAD family of products has been enhanced in the 16.3 release. By boosting performance and productivity through new features and functionality, this latest release helps deliver shorter, more predictable design cycles for PCB designs.

#### Join EMA for a Free 16.3 Lunch 'n Learn

To learn more about the OrCAD Release 16.3 attend a free "Lunch 'n Learn" in your area. You can register by visiting www.ema-eda.com/orcad16.3 or call us at 800.813.7288.

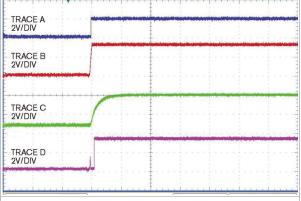

larger company wanted separate development tools for each target processor because it not only had more development resources but also planned to incorporate some innovations into its algorithm implementation that required the company's designers to be able to see deeply into the target system.